1、VDD_CPU_LIT覆铜宽度需满足需求,连接到芯片电源管脚的覆铜足够宽,路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源

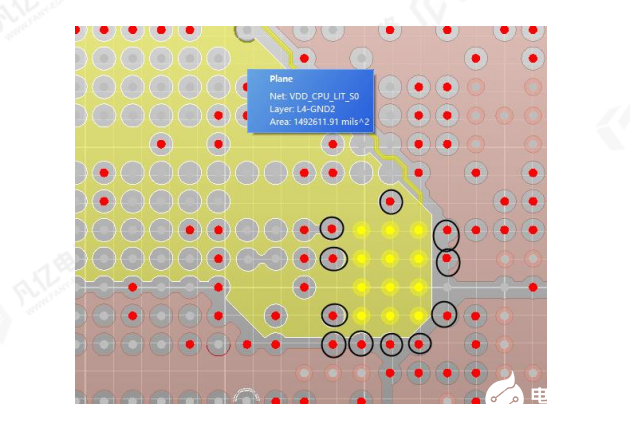

2、VDD_CPU_LIT的电源在外围换层时,要尽可能的多打电源过孔(9个以上0.5*0.3mm的过孔),降低换层过孔带来的压降;去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用。

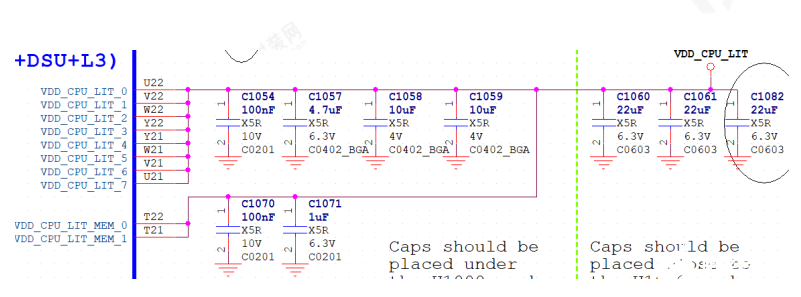

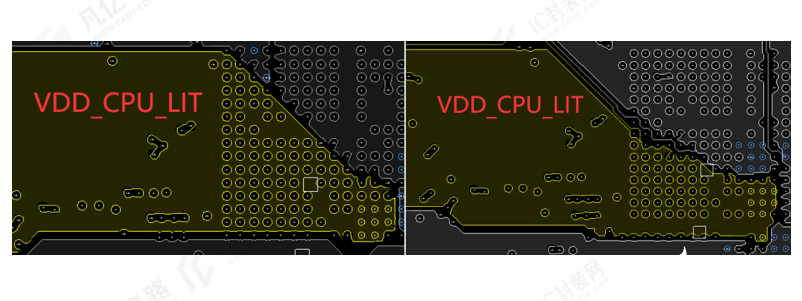

3、如图1所示,原理图上靠近RK3588的VDD_CPU_LIT电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容的GND PAD尽量靠近芯片中心的GND管脚放置,如图2所示。其余的去耦电容尽量摆放在RK3588芯片附近,并需要摆放在电源分割来源的路径上。

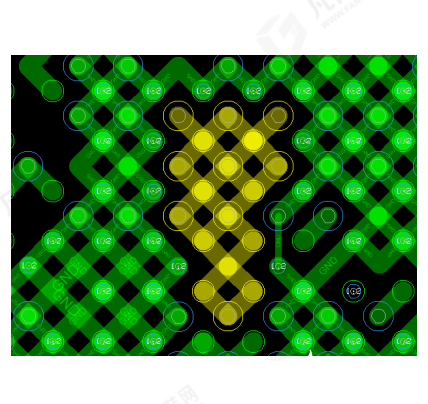

4、RK3588芯片VDD_CPU_LIT的电源管脚,每个管脚就近有一个对应过孔,并且顶层走“井”字形,交叉连接,如图3所示,建议走线VDD_CPU_LIT的原理图电源管脚去耦电容

5、VDD_CPU_LIT电源在CPU 区域线mil,外围区域宽度不小于300mil,采用双层电源覆铜方式,降低走线带来压降(

6、电源过孔40mil范围(过孔中心到过孔中心间距)内的GND过孔数量,建议≧9个。如图5所示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉

S EVB解读 /

。 本次内容篇幅较长,被分成了上下两部分,感兴趣的朋友可以关注公众号【华秋DFM】,并搜索《

汇总(上) /

推荐叠层及阻抗设计 /

注意事项 /

具有强大计算能力,图像处理能力,多接口显示,丰富接口传输能力。为了减少在高速信号传输过程中的反射现象,必须在信号源、接收端以及传输线上保持阻抗

s的区别 Rockchip是一家专业的半导体公司,成立于2001年,总部位于中国深圳,主要从事集成电路的设计、开发和销售。他们的热门产品

芯片是一款采用台积电TSMC 8纳米工艺制造的SoC,集成了4个高性能的Arm Cortex-A76